# ES0001

Errata Sheet

# AT32F415 device limitations

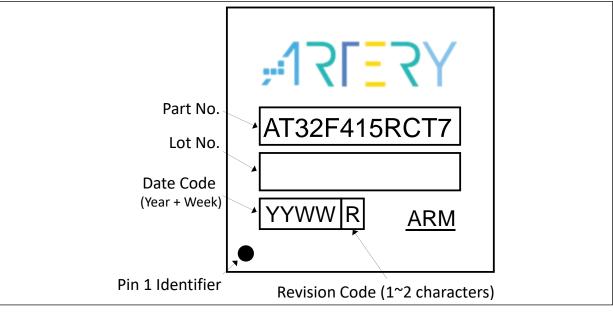

# **Device identification**

This errata sheet applies to Artery's AT32F415 series microcontrollers based on an ARM<sup>™</sup> 32-bit Cortex®-M4 core.

The full list of part numbers is shown in Table 2. The products are identifiable as shown in table 1:

• by the revision code marked below the lot number on the device package

| Table 1. Device identification |                                 |  |

|--------------------------------|---------------------------------|--|

| Part number                    | Revision code printed on device |  |

| AT225415                       | "B"                             |  |

| AT32F415                       | "C"                             |  |

- The Bit [78:76] Mask\_Version in the device capacity and unique ID (UID base address 0x1FFF F7E8) shows the revision code of the device. That is, the bit [6:4] at the address 0x1FFF7F1 can be used to get the revision code, for example Revision B: 0b001 Revision c: 0b010

- 2. Refer to *Chapter* 2 for details on how to identify the revision code on the different packages.

| Devices  | Flash memory | Part numbers                                                                   |

|----------|--------------|--------------------------------------------------------------------------------|

| AT32F415 | 256 KB       | AT32F415RCT7, AT32F415RCT7-7,<br>AT32F415CCT7, AT32F415CCU7,<br>AT32F415KCU7-4 |

|          | 128 KB       | AT32F415RBT7, AT32F415RBT7-7,<br>AT32F415CBT7, AT32F415CBU7,<br>AT32F415KBU7-4 |

|          | 64 KB        | AT32F415R8T7, AT32F415R8T7-7,<br>AT32F415C8T7, AT32F415K8U7-4                  |

#### Table 2. Device summary

# Contents

| 1 | AT3 | 2F415 device limitations                                                                              | 7  |

|---|-----|-------------------------------------------------------------------------------------------------------|----|

|   | 1.1 | ADC                                                                                                   | 8  |

|   |     | 1.1.1 ADC regular group conversion error due to preempted group configuration change.                 | 8  |

|   |     | 1.1.2 Unable to clear and set ADC preempted channel conversion end flag                               | 8  |

|   | 1.2 | CAN                                                                                                   | 9  |

|   |     | 1.2.1 Bit stuffing error causes the next data out of order during CAN communication                   | 9  |

|   |     | 1.2.2 Failed to filter RTR bit of standard frame in 32-bit identifier mask mode1                      | 2  |

|   |     | 1.2.3 CAN sends unexpected messages in case of narrow pulse disturbance on BS21                       | 3  |

|   |     | 1.2.4 Fail to cancel mailbox transmit command when CAN bus disconnected1                              | 3  |

|   | 1.3 | ERTC                                                                                                  | 4  |

|   |     | 1.3.1 How to enable wakeup event output on TAMPER PIN1                                                | 4  |

|   |     | 1.3.2 How to update TIME and DATE register value1                                                     | 4  |

|   |     | 1.3.3 3 to 6 LEXT clock cycles delay after each system reset when LEXT as ERTC cloc                   | зk |

|   |     | source1                                                                                               | 5  |

|   | 1.4 | GPIO 1                                                                                                | 5  |

|   |     | 1.4.1 PC0~5 pull-down resistors are turned on abnormally1                                             | 5  |

|   |     | 1.4.2 FT (5V tolerant pin) maintains at intermediate level in floating input mode1                    | 5  |

|   | 1.5 | I2S1                                                                                                  | 5  |

|   |     | 1.5.1 Failed to resume communication when I2S CK line is interfered1                                  | 5  |

|   |     | 1.5.2 I2S Philips protocol Start Frame data error under certain conditions1                           | 6  |

|   |     | 1.5.3 The first received data is misaligned in I2S PCM standard long frame receive-on mode1           | -  |

|   |     | 1.5.4 UDR flag is set mistakenly in I2S slave transmission mode and discontinuou communication state1 |    |

|   |     | 1.5.5 Data reception error when I2S 24-bit data is packed into 32-bit format                          | 6  |

|   | 1.6 | OTG 1                                                                                                 | 7  |

|   |     | 1.6.1 VBUS (PA9) cannot be released to other peripherals in OTG FS Device mode1                       | 7  |

|   | 1.7 | PWC1                                                                                                  | 7  |

|   |     | 1.7.1 PVM event generation after PVM enable when VDD is above PVM threshold1                          | 7  |

|   |     | 1.7.2 Unable to wakeup Deepsleep mode after AHB frequency division                                    |    |

|   |     | 1.7.3 Systick interrupt wakes up Deepsleep mode mistakenly1                                           |    |

|   |     | 1.7.4 Waking up Deepsleep mode while Deepsleep mode is being entered cause                            |    |

# **17[27**]

# AT32F415 Device Limitations

|      |        | instruction operation exception                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 18    |

|------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

|      | 1.7.5  | SWEF flag is set when enabling a standby-mode wakeup pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 18    |

|      | 1.7.6  | Unable to configure system clock after waking up Deepsleep mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19    |

|      | 1.7.7  | How to save more power during Run and Sleep mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 19    |

|      | 1.7.8  | $V_{\text{BAT}}$ powered domain register power-on reset failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19    |

| 1.8  | SPI    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 20  |

|      | 1.8.1  | Data reception transfer DMA request fails to be cleared by reading DT register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 20    |

|      | 1.8.2  | CS failing edge was not synchronized in slave SPI hardware CS mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20    |

| 1.9  | TMR    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 20  |

|      | 1.9.1  | Suspend mode failed in external clock mode B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20    |

|      | 1.9.2  | How to clear TMR-triggered DAM requests                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 20    |

|      | 1.9.3  | TMR overrun in encoder mode counter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21    |

|      | 1.9.4  | TMR accessing 0x4C address with DMA causes DMA request error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 21    |

|      | 1.9.5  | Slave timer unable to receive reset signal from master timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 22    |

|      | 1.9.6  | Break input failed when TMREN=0 (TMR disabled)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22    |

|      | 1.9.7  | Fail to generate CxORAW clear event when dead-time is disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 22    |

| 1.10 | USAF   | אד                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | . 23  |

|      | 1.10.1 | Enabling USART3 and TMR1/TMR3 causes PA7 error                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 23    |

|      | 1.10.2 | USART failed to receive data in IrDA mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 23    |

|      | 1.10.3 | Clearing TDC flag immediately after USART initialization causes data transfer e                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | error |

|      |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23    |

|      | 1.10.4 | Clearing RDBF bit only by reading data register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 23    |

|      | 1.10.5 | USART can still receive data using DMA in silent mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24    |

| 1.11 | WWD    | Т                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | . 24  |

|      | 1.11.1 | Unable to clear RLDF flag while using WWDT interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 24    |

| 1.12 | WDT.   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 24  |

|      | 1.12.1 | Entering Standby mode immediate after enabling WDT will trigger a reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24    |

|      | 1.12.2 | Entering Deepsleep mode immediately after enabling WDT causes WDT enabling wDT enabling wDT causes wDT enabling wDT ena |       |

|      |        | failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 24    |

| 1.13 | CRM    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 25  |

|      | 1.13.1 | CLKOUT clock output exception after entering Deepsleep mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25    |

|      |        | PLL 2x or 3x multiplication factor failure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       |

| 1.14 | I2C    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | . 25  |

|      | 1.14.1 | I2C slave communication error when APB equals or less than 4MHz                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 25    |

|      | 1.14.2 | I2C communication error when BUSERR is detected on bus                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 25    |

# AT32F415 Device Limitations

| 3 | Revision history                             | 27   |

|---|----------------------------------------------|------|

| 2 | Revision code on device marking              |      |

|   | 1.15.1 SLib and boot memory AP mode settings | 26   |

|   | 1.15 FLASH                                   | . 26 |

# List of tables

| Table 1. Device identification             | 1  |

|--------------------------------------------|----|

| Table 2. Device summary                    | 1  |

| Table 3. Summary of the device limitations | 7  |

| Table 4. Document revision history         | 27 |

# List of figures

| Figure 1. Package label (top view). |  |

|-------------------------------------|--|

|-------------------------------------|--|

# 1 AT32F415 device limitations

Table 3 gives a list of limitations that have been identified so far on the AT32F415 devices.

| Section  | Description                                                                                                  | Revision B | Revision C |

|----------|--------------------------------------------------------------------------------------------------------------|------------|------------|

| 1.1 ADC  | 1.1.1 ADC regular group conversion error due to preempted group configuration change.                        | Fail       | Fixed      |

|          | 1.2.1 Bit stuffing error causes the next data out of order during CAN communication.                         | Fail       | Fail       |

|          | 1.2.2 Failed to filter RTR bit of standard frame in 32-bit identifier mask mode.                             | Fail       | Fail       |

| 1.2 CAN  | 1.2.3 CAN sends unexpected messages in case of narrow pulse disturbance on BS2.                              | Fail       | Fail       |

|          | 1.2.4 Fail to cancel mailbox transmit command when CAN bus disconnected                                      | Fail       | Fail       |

|          | 1.3.1 How to enable wakeup event output on TAMPER PIN.                                                       | Fail       | Fixed      |

| 1.3 ERTC | 1.3.2 How to update TIME and DATE register value.                                                            | Fail       | Fail       |

|          | 1.3.3 3 to 6 LEXT clock cycles delay after each system reset when LEXT as ERTC clock source.                 | Fail       | Fixed      |

| 1.4 GPIO | 1.4.1 PC0~5 pull-down resistors are turned on abnormally.                                                    | Fail       | Fixed      |

|          | 1.4.2 FT (5V tolerant pin) maintains at intermediate level in floating input mode                            | Fail       | Fail       |

|          | 1.5.1 Failed to resume communication when I2S CK line is interfered.                                         | Fail       | Fixed      |

|          | 1.5.2 I2S Philips protocol Start Frame data error under certain conditions.                                  | Fail       | Fixed      |

| 1.5 I2S  | 1.5.3 The first received data is misaligned in I2S PCM standard long frame receive-<br>only mode.            | Fail       | Fail       |

|          | 1.5.4 UDR flag is set mistakenly in I2S slave transmission mode and discontinuous communication state.       | Fail       | Fail       |

|          | 1.5.5 Data reception error when I2S 24-bit data is packed into 32-bit format.                                | Fail       | Fail       |

| 1.6 OTG  | 1.6.1 VBUS (PA9) cannot be released to other peripherals in OTG_FS Device mode.                              | Fail       | Fixed      |

|          | 1.7.1 PVM event generation after PVM enable when VDD is above PVM threshold.                                 | Fail       | Fail       |

|          | 1.7.2 Unable to wakeup Deepsleep mode after AHB frequency division.                                          | Fail       | Fail       |

|          | 1.7.3 Systick interrupt wakes up Deepsleep mode mistakenly.                                                  | Fail       | Fail       |

| 1.7 PWC  | 1.7.4 Waking up Deepsleep mode while Deepsleep mode is being entered causes instruction operation exception. | Fail       | Fixed      |

|          | 1.7.5 SWEF flag is set when enabling a standby-mode wakeup pin.                                              | Fail       | Fixed      |

|          | 1.7.6 Unable to configure system clock after waking up Deepsleep mode.                                       | Fail       | Fail       |

|          | 1.7.7 How to save more power during Run and Sleep mode.                                                      | Fail       | Fixed      |

|          | 1.7.8 VBAT powered domain register power-on reset failure                                                    | Fail       | Fail       |

| 1.8 SPI  | 1.8.1 Data reception transfer DMA request fails to be cleared by reading DT register.                        | Fail       | Fail       |

| 1.0 361  | 1.8.2 CS failing edge was not synchronized in slave SPI hardware CS mode.                                    | Fail       | Fail       |

|          | 1.9.1 Suspend mode failed in external clock mode B.                                                          | Fail       | Fixed      |

|          | 1.9.2 How to clear TMR-triggered DAM requests                                                                | Fail       | Fixed      |

|          | 1.9.3 TMR overrun in encoder mode counter.                                                                   | Fail       | Fixed      |

| 1.9 TMR  | 1.9.4 TMR accessing 0x4C address with DMA causes DMA request error.                                          | Fail       | Fixed      |

|          | 1.9.5 Slave timer unable to receive reset signal from master timer                                           | Fail       | Fail       |

|          | 1.9.6 Break input failed when TMREN=0 (TMR disabled)                                                         | Fail       | Fail       |

|          | 1.9.7 Fail to generate CxORAW clear event when dead-time is disabled                                         | Fail       | Fail       |

|          | 1.10.1 Enabling USART3 and TMR1/TMR3 causes PA7 error.                                                       | Fail       | Fixed      |

| 1.10     | 1.10.2 USART failed to receive data in IrDA mode.                                                            | Fail       | Fixed      |

| USART    | 1.10.3 Clearing TDC flag immediately after USART initialization causes data transfer error.                  | Fail       | Fixed      |

|          | 1.10.4 Clearing RDBF bit only by reading data register.                                                      | Fail       | Fixed      |

#### Table 3. Summary of the device limitations

# ,**:17[**7]

# AT32F415 Device Limitations

| Section   | Description                                                                              |      | Revision C |

|-----------|------------------------------------------------------------------------------------------|------|------------|

|           | 1.10.5 USART can still receive data using DMA in silent mode.                            | Fail | Fail       |

| 1.11 WWDT | 1.11.1 Unable to clear RLDF flag while using WWDT interrupts.                            | Fail | Fixed      |

|           | 1.12.1 Entering Standby mode immediate after enabling WDT will trigger a reset.          | Fail | Fixed      |

| 1.12 WDT  | 1.12.2 Entering Deepsleep mode immediately after enabling WDT causes WDT enable failure. | Fail | Fixed      |

| 1 12 0014 | 1.13.1 CLKOUT clock output exception after entering Deepsleep mode.                      | Fail | Fail       |

| 1.13 CRM  | 1.13.2 PLL 2x or 3x multiplication factor failure.                                       | Fail | Fail       |

| 4.44.100  | 1.14.1 I2C slave communication error when APB equals or less than 4MHz                   | Fail | Fail       |

| 1.14 I2C  | 1.14.2 I2C communication error when BUSERR is detected on bus                            | Fail | Fail       |

| 1.15      | 1.15.1 SLib and boot memory AP mode settings     Fail     Fail                           |      | Fail       |

# 1.1 ADC

# 1.1.1 ADC regular group conversion error due to preempted group configuration change

• Description:

In ADC sequential and repetition conversion mode of regular group, attempting to change channel configuration of preempted group during a regular group conversion will cause regular group conversion data out of order.

For example, when the regular group is converting the channel 1, 2, 3 and 4, attempting to change preempted group configuration during channel-2 conversion will have the channel 2 converted twice, which results in the convertion order of regular group to be 1, 2, 2, 3, and 4.

Workaround:

When using multi-channels for regular and preempted conversion simultaneously, do not try to change its channel configuration after preempted group is configured.

Revision plan:

Revision C has fixed this issue.